计组体系构建----有关存储、指令与计算

计组体系构建—-有关存储、指令与计算

问题引出:什么是存储字长?

我们通常说

- “存储体由存储单元组成,存储单元可存储一串二进制代码,称这段代码为存储字,这串代码的位数为存储字长,存储字长可以是1B(8bit)(字节)的偶数倍”

但是此处的存储单元中英文互联网及教材中都没有给出明确的定义。且中文教材中用词歧义较多

- 英文教材称其为

memory unit,中文直译过来就是存储单元

- 英文教材称其为

而一般说来,

MDR的位数与存储字长相等,MDR是CPU中存放数据的寄存器到此处需要继续引出概念

机器字长:CPU进行一次整数运算所能处理的二进制数据位数(通常和ALU直接相关)数据总线宽度:能一次并行传输的数据位数,一般等于机器字长

引出主要概念后,可以发现,存储字长与机器字长的概念界限是较为模糊的,不过也是可以思考出来,存储字长一般与机器字长通常是相同的。

但真的有这么简单么?

现代计算机通常

按字节编址,存储字长是字节的整数倍,比如存储字长32位是4字节。(以下预设计算机机器字长、数据总线宽度和存储字长均为32位)- 假设一条指令长度为一个存储字长32位,计算机进行一次

取指周期后就要将其取出。- 一个存储字长是四个字节,也就是在主存地址空间中占用了

四个地址。CPU访问内存是通过地址来进行存储单元的访问的。 - 同时我们也知道,一般来讲,机器对内存的访问时间是最长的,指令执行的机器周期一般会以存取周期为依据来划分,所以一次取指周期已经属于指令执行过程中的最长周期了。

- 一个存储字长是四个字节,也就是在主存地址空间中占用了

- 此处显而易见的产生了一个矛盾

- CPU读一次地址,读取一个

存储单元中的数据。 - 那么4个字节的存储字,就要读四次数据吗?那不就是要经过四个存取周期吗?

- 显然不是。

- CPU读一次地址,读取一个

- 非常明确的是,此处还有另外一个矛盾

- 一个字节8位,但是数据总线宽度却有32位,有24位没有使用,浪费了吗?

- 基于此,我们引入

位扩展- 32位数据总线的宽度大于8位存储芯片的字长,使用位扩展对存储芯片进行扩位,比如并联4个8位存储芯片,将其扩展到32位

- 这样,就解决了一个矛盾,令数据的位数与CPU的位数相等

- 但是最根本的矛盾,地址与数据的矛盾没有解决。此时计算机依然是按地址顺序读取指令,位扩展没有实质性的作用。这才是关键的问题。

- 此时我们引入

多体并行存储器、流水线技术以及突发传输技术 - 多体并行存储器中的

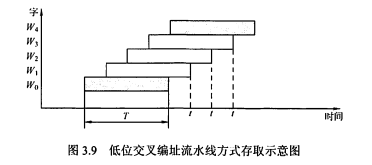

低位交叉编址,配合流水线技术,能够以接近一个存取周期的时间来进行多地址数据的存取 - 再结合

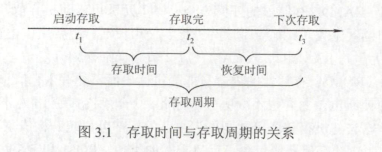

突发传输技术,就能够成功使CPU在读取一个地址的情况下,连续传输多个地址的存储单元突发传输:数据在连续的内存地址范围内以连续的方式进行传输。传输时只需读取首地址,就可以连续读取后续连续地址范围的一批数据。低位交叉编址与流水线:由于存储器在每次存取后都有一定的恢复时间,使得串行存取的速度慢、效率低。![262395959-599fb0d5-a748-4ab1-84ea-de10932bcb44.png (382×152) (user-images.githubusercontent.com)]()

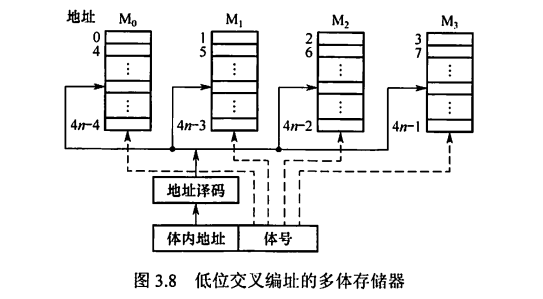

- 引入低位交叉编址,将连续地址的存储单元存放在不同的存储体中,并行存取,提高带宽

![262396251-ad341ff7-6847-4dc7-916d-082771f32264.png (543×299) (user-images.githubusercontent.com)]()

![262396219-8c687d85-d9e5-4182-80ec-8da9061e1c99.png (372×165) (user-images.githubusercontent.com)]()

- 此时我们引入

- 通过上述技术,我们成功实现了在存储单元的大小与机器字长不匹配的情况下,现代按字节编址的计算机如何实现通过一个地址来读取一条指令的。

- 但是是否发现,本文中有关存储单元的定义十分模糊?

- 回到我们最初的引入,究竟什么是存储单元?

- 一个字存储单元,占一个存储字长

- 还是一个字节存储单元,占据一个字节?

- 很明显,两个都正确。

- 回到我们最初的引入,究竟什么是存储单元?

- 在我个人的分析下,一般来讲,在408中

- 物理层面的存储单元,多为字节存储单元,如上述的低位交叉编址方式中的存储单元

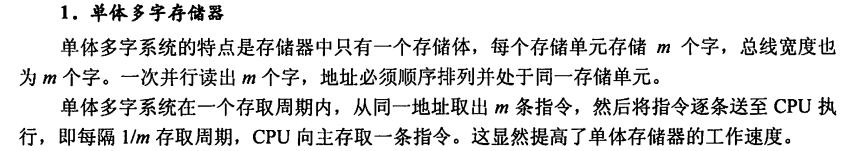

- 逻辑层面,与机器字长、数据和存储等概念挂钩的,多为字存储单元,也就是一个存储字长,如单体多字存储器

![262399532-23b7c9b3-c98c-4ea4-90b1-1547e951ff8c.png (854×151) (user-images.githubusercontent.com)]()

- 同时,还有一个显而易见的方面就是

- 读取的存储字如果不是存储字的长度的话,那么数据的按边界对齐方式存储将毫无意义。

- 假设一条指令长度为一个存储字长32位,计算机进行一次

延申问题

- 一般以指令的取指周期作为机器周期,但是条件是指令字长等于存储字长

- 若指令长度等于多个机器字长,会影响访存时间。如双字长指令,需要进行两次访存

双字长指令:指令长度等于两个机器字长

取指周期=指令所占存储单元数×存取周期 =(指令的长度/存储字的长度)×主存的读/写周期- 所以不如更严谨的说是以一个存储字长的

存取周期为机器周期

- 若指令长度等于多个机器字长,会影响访存时间。如双字长指令,需要进行两次访存

- 承接上点,CPU执行访存可能会执行多次,因为指令可能会长于机器字长

- 一般以指令的取指周期作为机器周期,但是条件是指令字长等于存储字长

由于本人在中文互联网难以找到相关论述资料,以上观点仅为对408计算机组成原理内容的大致分析、思考和猜想。